2000元阿里云代金券免费领取,2核4G云服务器仅664元/3年,新老用户都有优惠,立即抢购>>>

阿里云采购季(云主机223元/3年)活动入口:请点击进入>>>,

阿里云学生服务器(9.5元/月)购买入口:请点击进入>>>,

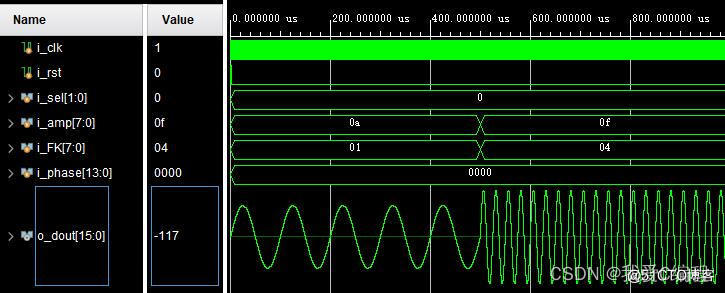

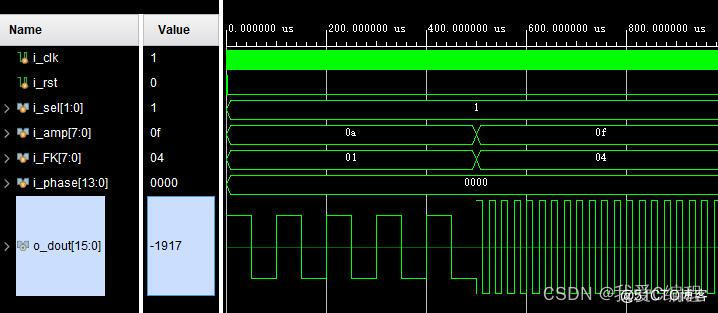

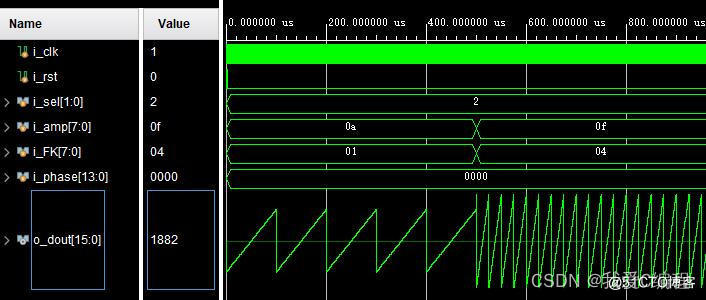

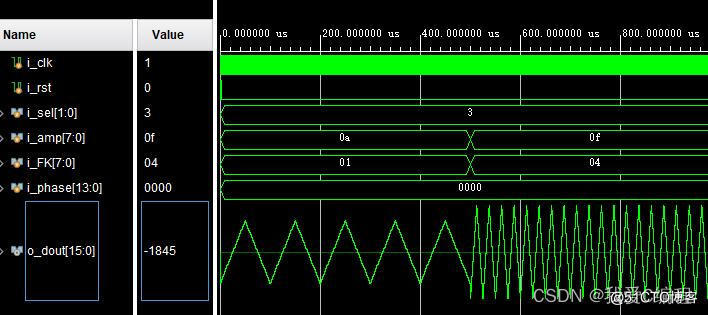

1.算法仿真效果

vivado2019.2仿真结果如下:

输出正弦,并改变幅度,频率等。

输出方波,并改变幅度,频率等。

输出锯齿波,并改变幅度,频率等。

输出三角波,并改变幅度,频率等。

2.算法涉及理论知识概要

DDS(Direct Digital Synthesis,直接数字频率合成)技术是一种通过高性能数字计数器和查找表技术生成高精度、灵活可控的模拟信号的手段。DDS多功能信号发生器可以输出正弦波、方波、锯齿波、三角波等多种波形,并能够方便地调整波形类型、幅度、频率和初始相位。以下是DDS信号发生器的详细原理及其相关数学公式。

2.1 DDS基本原理

DDS信号发生器的核心部件包括高速累加器、波形存储器(查找表)和数模转换器(DAC)。

高速累加器:每次时钟周期,累加器都会将输入的频率控制字(Frequency Control Word, FCW)与前一周期的累加结果相加。频率控制字决定了输出信号的频率。

ACCUMULATOR:N(t)=N(t?1)+FCW

其中,N(t) 是在时间t 时刻的累加器输出,FCW 是频率控制字,决定了输出信号的频率。

波形存储器(查找表):累加器的输出值会被当作地址,用于查询预先存储在波形存储器中的幅度数据。对于正弦波,存储器中的数据是对正弦函数的离散采样;对于方波、锯齿波、三角波等其他波形,存储的是这些波形在固定区间内的离散值。

LUT:X[N(t)]

其中,X 是波形存储器,N(t) 作为地址,取出对应的幅度值。

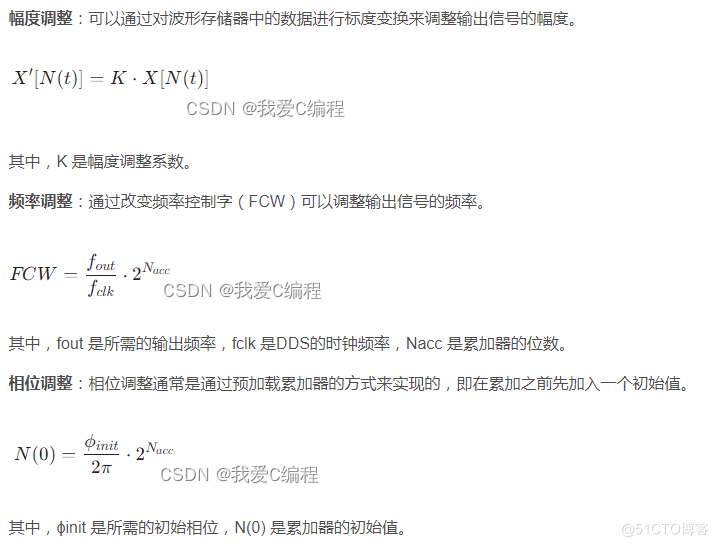

2.2 波形参数调整

DDS多功能信号发生器利用高速累加器、波形存储器和数模转换器,通过调整频率控制字、波形存储器的内容以及累加器的初始值,可以灵活地生成各种波形,并精确控制其幅度、频率和初始相位。这项技术因其高度的灵活性和优异的频率分辨率,在通信、测量仪器、雷达、声纳等诸多领域有着广泛应用。

3.Verilog核心程序

````timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/04/01 15:42:00

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

module TEST();

reg i_clk;

reg i_rst;

reg[1:0]i_sel;//信号选择00,01,10,11

reg[7:0]i_amp;//调整幅度,设置1~16,小于8缩小,大于8放大,等于8不变

reg[7:0]i_FK; //调整频率,1最慢,逐渐增加

reg[13:0]i_phase;//初始相位

wire signed[15:0]o_dout;

tops uut(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (i_sel),//信号选择00,01,10,11

.i_amp (i_amp),

.i_FK (i_FK),

.i_phase (i_phase),

.o_dout (o_dout)

);

initial

begin

i_clk = 1'b1;

i_rst = 1'b1;

i_sel = 2'b11;

i_amp = 5'd10;

i_FK = 8'd1;

i_phase = 14'd0;

#1000

i_rst = 1'b0;

#500000

i_amp = 5'd15;

i_FK = 8'd4;

end

always #5 i_clk=~i_clk;

endmodule

```