2000元阿里云代金券免费领取,2核4G云服务器仅664元/3年,新老用户都有优惠,立即抢购>>>

阿里云采购季(云主机223元/3年)活动入口:请点击进入>>>,

阿里云学生服务器(9.5元/月)购买入口:请点击进入>>>,

在之前了解 PN 结以及逻辑电路实现之后,终于可以开始尝试实现计算机的加法了。

- 逻辑门,包括与、或、与非、异或

- 半加器,半加器电路

- 全加器,全加器电路

- 波纹进位加法器

逻辑门

与门 AND

或门 OR

与非门 NAND

异或门 XOR

真值表

| A | B | AND | OR | NAND | XOR |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

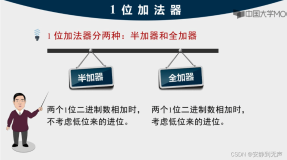

半加器

半加器(half adder)的功能是将两个一位二进制数相加。它具有两个输入和两个输出(分别是和(sum)、进位(carry))。

— Wiki

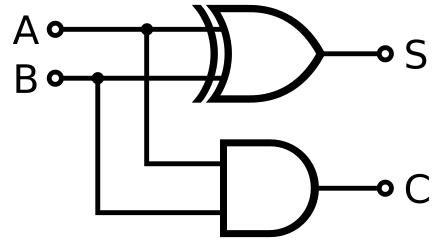

半加器电路图

| A | B | Carry | Sum |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

半加器简化图

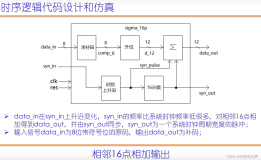

全加器

全加器(full adder)将两个一位二进制数相加,并根据接收到的低位进位信号,输出和、进位输出。全加器的三个输入信号为两个加数A、B和低位进位Cin。

全加器逻辑电路

该电路如用简化版半加器表示,可以如下图:

全加器真值表

二进制的全加器,刚可以用两位表示最大值,即 1 + 1 + 1 = 3 = 11(2)

| A | B | Cin | Cout | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

全加器简化图

或

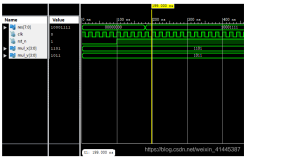

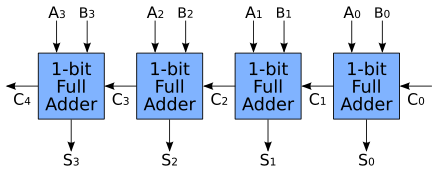

波纹进位加法器

如果不需要连接其他进位信号,则最低位的全加器可以用半加器替换。

References

更多文章访问:zhoukekestar.github.io/notes